Mecánica Computacional Vol XXVIII, págs. 2943-2953 (artículo completo) Cristian García Bauza, Pablo Lotito, Lisandro Parente, Marcelo Vénere (Eds.) Tandil, Argentina, 3-6 Noviembre 2009

# EVALUACIÓN DE LA CAPACIDAD DEL TEST BASADO EN TRANSITORIO PARA DETECTAR FALLAS DE DEGRADACIÓN

# José Peralta<sup>a</sup>, Mónica Lovay<sup>a</sup>, Gabriela Peretti<sup>a,b</sup>, Eduardo Romero<sup>a,b</sup>, Carlos Marqués<sup>b</sup>

<sup>a</sup> Grupo de Estudios en Calidad en Mecatrónica, GECAM, UTN, Facultad Regional Villa María, Avda. Universidad 450, (5900) Villa María, Córdoba, Argentina, depelectronica@yahoo.com.ar

Palabras clave: Electrónica espacial, fallas, test, test por análisis de transitorio

Abstract. Los efectos de la radiación ionizante sobre los componentes de la electrónica espacial, en particular las consecuencias de las dosis acumuladas, son muy significativos. Una desviación progresiva en los valores de los parámetros circuitales por estas causas, conducen a la degradación del desempeño de la aplicación completa. En los sistemas espaciales se debe recurrir a un test periódico que permita en todo momento determinar si los componentes se han degradado lo suficiente como para poner en peligro dichas aplicaciones. La simplicidad conceptual del denominado test por análisis de transitorio (TRAM), en conjunción con las magnitudes relativamente simples de medir, lo hacen sumamente atractivo para aplicaciones de test en campo. En este trabajo, utilizando un modelo de falla basado en especificaciones, se analiza la capacidad de distintos atributos de test para la detección de fallas, adoptando como casos de estudio dos filtros de tiempo continuo de segundo orden. Debido a que las aplicaciones que se persiguen son las espaciales, la atención se centrará en maximizar la cobertura de fallas. Para los casos considerados los resultados de simulación de fallas indican que TRAM puede alcanzar una excelente cobertura de fallas, con lo que su empleo en aplicaciones de alta criticad es interesante. No obstante, una alta probabilidad de falsos positivos podría complicar la aplicación de esta estrategia.

<sup>&</sup>lt;sup>b</sup> Grupo de Desarrollo Electrónico e Instrumental, Facultad de Matemática, Astronomía y Física, Universidad Nacional de Córdoba, Medina Allende y Haya de Torre (5000) Córdoba, Argentina, marques@famaf.unc.edu.ar

### 1 INTRODUCCIÓN

Es bien conocida la susceptibilidad de los componentes electrónicos a la radiación ionizante presente en el medioambiente espacial. Numerosos trabajos se han publicado sobre una diversidad de efectos entre los que merecen citarse efectos por dosis total (TID, *Total Ionization Dose*), efectos transitorios únicos (SET, *Single Event Transient*), efectos transitorios únicos en analógicos (ASET, *Analog Single Event Transient*) y eventos únicos de ruptura de compuerta (SEGR, *Single Event Gate Rupture*) (Holmes- Siedle y Adams, 2002; Schrimpf y Fleetwood, 2004).

En particular, los efectos de dosis acumulada son muy significativos ya que producen una desviación progresiva en los valores de los parámetros circuitales que conducen a la degradación del desempeño de la aplicación completa (Axness et al., 1991; Oldham y McLean, 2003; Barnaby, 2006). En aplicaciones espaciales, en donde el mantenimiento es imposible o muy difícil de realizar, se debe recurrir a un test periódico que permita en todo momento determinar si los componentes se han degradado lo suficiente como para poner en peligro la aplicación. Si esto fuese así, normalmente se recurre a alguna forma de reconfiguración circuital que, utilizando recursos redundantes o configurando de manera distinta a los existentes, logre un desempeño que permita continuar con la misión.

Uno de los bloques analógicos más extensamente utilizados en todo tipo de aplicaciones son los filtros. Por esta razón, el test de filtros analógicos, digitales y de señales mixtas ha sido objeto de numerosos trabajos de investigación, generándose numerosas estrategias tanto para el test de producción como para el test en campo. Una de las más interesantes por su simplicidad conceptual y de implementación es la propuesta por Calvano et al. (1999, 2000) denominada Test por Análisis de Transitorio (TRAM). Esta metodología se aplica a filtros de segundo orden o superior diseñados como cascada de estos y consiste en excitar el circuito con un escalón, rampa o parábola y evaluar ciertos parámetros de la respuesta transitoria denominados atributos de test.

TRAM se orientó primero al test funcional y posteriormente se la evaluó para la detección de fallas de desviación. Sin embargo, sólo recientemente se ha estudiado la capacidad TRAM para la detección de fallas paramétricas utilizando diferentes modelos de fallas (Peralta et al., 2007, 2009). Las coberturas de fallas encontradas, en algunos casos, son mucho menores que las previamente reportadas usando otros modelos de fallas. Es de destacar que estas evaluaciones sólo consideran como atributos de test al tiempo de ocurrencia del pico y a la sobre-elongación de la respuesta transitoria, razón por la que surge la necesidad de considerar otros parámetros para mejorar el desempeño de la estrategia.

En este trabajo se analiza la capacidad de distintos atributos de test para la detección de fallas, adoptando como casos de estudio dos filtros de tiempo continuo de segundo orden. Debido a que las aplicaciones últimas que se persiguen son las espaciales, la atención se centrará en maximizar la cobertura de fallas. De esta forma, se asume que los circuitos a testear en la aplicación han superado exitosamente los tests de producción. Los resultados de las campañas de inyección de fallas demuestran que es posible mejorar significativamente la métrica de interés aumentando la cantidad de atributos medidos en la aplicación de TRAM.

### 2 TEST BASADO EN TRANSITORIO

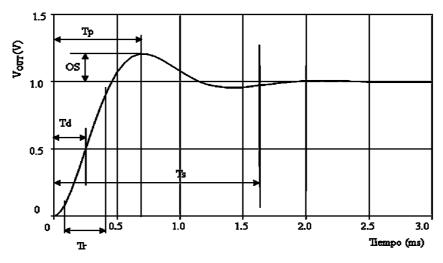

Tal como se mencionó arriba, la idea central de esta estrategia es excitar al sistema bajo test (filtros de segundo orden), con una señal de entrada que cause un transitorio sub-amortiguado y asumir que la presencia de fallas en el filtro provocará un cambio en el tiempo de ocurrencia del pico (Tp) y en la sobre-elongación de dicho transitorio (OS). En este trabajo

se considerarán además otros parámetros adicionales con el objetivo de aumentar la cobertura de fallas. Estos son tiempo de demora (Td), tiempo de crecimiento (Tr) y tiempo de establecimiento (Ts). Todos los parámetros a ser considerados se indican en la Figura 1.

Figura 1: Curva de respuesta escalón unitario en la que se muestran Td, Tp, Ts, OS y Tr

Los valores de los atributos de test pueden obtenerse evaluando las expresiones (1) a (5) en las que  $\omega_n$  es la frecuencia natural no amortiguada y  $\zeta$  es el factor de amortiguamiento. Estos valores caracterizan la dinámica de un sistema de segundo orden.

$$Ts = -\frac{1}{\zeta} \cdot \frac{\log(0.05 \cdot \sqrt{1 - \zeta^2})}{\omega_n}$$

(1)

$$Tp = \frac{\pi}{\omega_n \cdot \sqrt{1 - \zeta^2}} \tag{2}$$

$$Tr = \frac{1 - 0.416 \cdot \zeta + 2.917 \cdot \zeta^2}{\omega_p}$$

(3)

$$Td = \frac{1.1 + 0.125 \cdot \zeta + 0.469 \cdot \zeta^2}{\omega_n}$$

(4)

$$OS = e^{-\pi \left(\frac{\zeta}{\sqrt{1-\zeta^2}}\right)}$$

(5)

Un análisis simple de la topología del filtro bajo test permite establecer las relaciones entre los parámetros  $\omega_n$  y  $\zeta$  y los componentes del filtro. Estas relaciones pueden observarse en las expresiones (6), (8) y (10) y (11) teniendo en cuenta que  $\omega_n$  y  $\omega_p$ , la frecuencia de polo, son equivalentes. Estas expresiones permiten determinar analíticamente los parámetros necesarios para definir la calidad del test, evitando la simulación del circuito. De esta forma, es posible disminuir notoriamente el costo computacional de las extensas campañas de inyección de fallas que son necesarias para la caracterización del test.

#### 3 FILTROS BAJO TEST

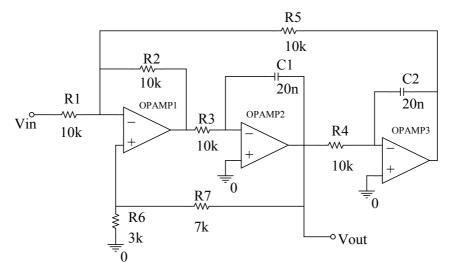

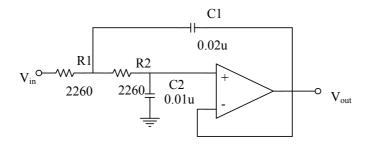

El primer caso de estudio es el filtro pasa-banda de la Figura 2 (Kaminska et al., 1997), mientras que el segundo caso se muestra en la Figura 3 (Savir y Guo, 2003). Estos circuitos se referencian en este trabajo como Filtro 1 y Filtro 2 respectivamente.

Figura 2: Primer filtro bajo test (Filtro 1)

Figura 3: Segundo filtro bajo test (Filtro 2)

Se denominan parámetros directos (PD) a aquellos relacionados con las especificaciones funcionales, en este caso el factor de calidad  $Q_p$  y la frecuencia de polo,  $\omega_p$ . Por otro lado, se denominan parámetros de bajo nivel a los valores de los componentes del circuito (en este caso resistencias y capacitores). Las expresiones (6) y (7) relacionan los parámetros directos con los componentes del Filtro 1, mientras que (8) y (9) son expresiones similares para el Filtro 2.

$$\omega_{pF1} = \sqrt{\frac{R_2}{C_2 \cdot R_4 \cdot C_1 \cdot R_3 \cdot R_5}} \tag{6}$$

$$Q_{pF1} = \sqrt{\frac{R_2}{C_2 \cdot R_4 \cdot C_1 \cdot R_3 \cdot R_5}} \cdot \frac{C_1 \cdot R_3 \cdot R_5 \cdot R_1 \cdot (R_6 + R_7)}{R_6 \cdot (R_5 \cdot R_1 + R_5 \cdot R_2 + R_2 \cdot R_1)}$$

(7)

$$\omega_{pF2} = \frac{1}{\sqrt{R_1 \cdot R_2 \cdot C_1 \cdot C_2}} \tag{8}$$

$$Q_{pF2} = \sqrt{\frac{C_1}{C_2}} \cdot \frac{\sqrt{R_1 \cdot R_2}}{R_1 + R_2} \tag{9}$$

Finalmente se denominan parámetros indirectos (PI) a los atributos de test, en este caso los dados por las ecuaciones (1) a (5). Para establecer los valores de los PI en relación con los de bajo nivel, además del valor de  $\omega_p$  se debe obtener el valor del coeficiente de amortiguamiento  $\zeta$  en función de los componentes del circuito, dado por las expresiones (10) y (11) para el Filtro 1 y para el Filtro 2 respectivamente.

$$\zeta_{\text{F1}} = \frac{R_6 \cdot (R_5 \cdot R_1 + R_5 R_2 + R_2 \cdot R_1)}{2 \cdot C_1 \cdot R_3 \cdot R_5 \cdot R_1 \cdot (R_6 + R_7)} \cdot \frac{1}{\sqrt{\frac{R_2}{C_2 \cdot R_4 \cdot C_1 \cdot R_3 \cdot R_5}}}$$

(10)

$$\zeta_{F2} = \sqrt{\frac{C_2}{4 \cdot C_1 \cdot R_2 \cdot R_1}} \cdot (R_1 + R_2)$$

(11)

# 4 METODOLOGÍA DE EVALUACIÓN DE LA EFECTIVIDAD DE LA ESTRATEGIA

En trabajos anteriores se caracterizó TRAM como test de producción, razón por la que se adoptó un modelo de degradación previamente utilizado por otros autores (Chaehoi et al., 2003; Raghunathan et al., 2004). Este modelo asume una degradación de los parámetros de bajo nivel que implica el aumento progresivo de la dispersión de cada uno de ellos.

En este trabajo un circuito se considera con falla sólo si viola alguna de las especificaciones debido a desviaciones estadísticas en los componentes (Liu y Ozev, 2007; Bounceur et al., 2007).

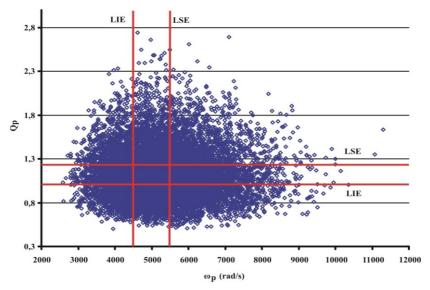

Para el caso de estudio adoptado se definen especificaciones sobre los PD  $\omega_p$  y  $Q_p$ . Con las ecuaciones (6), (7), (8) y (9) se calculan los valores nominales de estos parámetros utilizando los valores de R y C mostrados en los esquemas de la Figura 2 y Figura 3. Por otro lado, se admite aquí una tolerancia de  $\pm 10\%$  en los PD lo que permite obtener el límite inferior de especificaciones (LIE) y el límite superior de especificaciones (LSE) (Tabla 1). Debe mencionarse que estas tolerancias dependen de la aplicación y fueron fijadas aquí, arbitrariamente, con fines demostrativos.

| Parámetro directo | Filtro 1                        |       | Filtro 2           |       |

|-------------------|---------------------------------|-------|--------------------|-------|

| rarametro unecto  | $\omega_{\rm p}  ({\rm rad/s})$ | $Q_p$ | $\omega_p$ (rad/s) | $Q_p$ |

| LIE               | 4.5E+03                         | 1.000 | 2.82E+04           | 0.636 |

| Valor Nominal     | 5.0E+03                         | 1.111 | 3.13E+04           | 0.707 |

| LSE               | 5.5E+03                         | 1.222 | 3.44E+04           | 0.778 |

Tabla 1: Valores Nominales, LSE y LIE para los PD

Por otro lado, deben determinarse tolerancias sobre los PI a ser considerados durante el test. Éstas son de gran importancia, porque permiten declarar a un circuito como defectuoso si

se excede al menos una de ellas. Para esto es necesario caracterizar adecuadamente el comportamiento de los circuitos cuando no presentan fallas.

Se propone determinar estos límites mediante simulación Montecarlo considerando que todos los parámetros de bajo nivel se encuentran dentro de sus límites de tolerancia. Para ello se asume una distribución normal para cada uno de los componentes del circuito, con media igual al valor nominal y una dispersión (σ) del 3%. En la simulación se genera una población de 10000 individuos, cada uno caracterizado por el conjunto de valores de resistencias y capacidades generados aleatoriamente con los parámetros arriba indicados. Para cada individuo es posible calcular, mediante las fórmulas (6), (7), (8) y (9), los parámetros directos y clasificarlo como dentro de especificaciones o no. Se separa la población de circuitos dentro de especificaciones y se analizan para ésta los valores correspondientes de los PI mediante las expresiones (1) a (5). De este proceso se obtiene una distribución para cada atributo de test sobre los que se tienen que fijar límites de tolerancia. Para este fin se aplicaron a cada una de las distribuciones tests de normalidad usuales, que establecieron con un nivel de confianza de 95% desajustes marcados respecto a la distribución normal. Por este motivo se adoptaron límites de tolerancia no paramétricos (Mitra, 1998), que se reportan en Tabla 2.

| PI | Límites de Tolerancia No Paramétricos<br>(Intervalo de confianza al 95.0% para el 99.52% de la población) |          |          |          |

|----|-----------------------------------------------------------------------------------------------------------|----------|----------|----------|

|    | Filtro 1                                                                                                  |          | Filtro 2 |          |

| Тр | 6.32E-04                                                                                                  | 8.00E-04 | 1.28E-04 | 1.60E-04 |

| OS | 1.64E-01                                                                                                  | 2.44E-01 | 2.62E-02 | 6.84E-02 |

| Tr | 2.42E-04                                                                                                  | 3.33E-04 | 6.09E-05 | 7.83E-05 |

| Td | 2.26E-04                                                                                                  | 2.82E-04 | 4.15E-05 | 5.01E-05 |

| Ts | 1.18E-03                                                                                                  | 1.61E-03 | 1.35E-04 | 1.68E-04 |

Tabla 2: Límites de Tolerancias para los PI

Con el objetivo de evaluar la eficiencia de la estrategia de test para la detección de desviaciones en las especificaciones más allá de los límites tolerables, es necesario generar una población de circuitos que presenten diferentes grados de apartamiento de las especificaciones respecto de los valores tolerables. Una alternativa es desviar arbitrariamente los valores de los parámetros directos (Calvano et al., 2001). El problema de esta opción es que ignora la correlación entre estos parámetros, motivo por el que la inyección de desviaciones directamente en las especificaciones se hace poco realista.

En este trabajo se inyectan desviaciones en los parámetros de bajo nivel para provocar desviaciones en los PD, conduciendo a una simulación más realista. Se adoptó una distribución uniforme para cada uno de los parámetros de bajo nivel con límites de 30% del valor nominal. De esta forma se pretende generar una población con individuos que cumplan con las especificaciones y con otros que presenten diferentes apartamientos de las mismas. Esta población se obtiene mediante simulación Montecarlo. Consecuentemente las métricas obtenidas considerarán una diversidad de casos significativa, ponderando el test en diferentes situaciones.

Para cada individuo generado se obtienen, utilizando las expresiones (1) a (5) y (6) a (9), los parámetros indirectos y directos. De esta forma es posible determinar la probabilidad de

rechazar circuitos malos, o cobertura de fallas (CF) y la probabilidad de falsos positivos (PFP), circuitos buenos que son declarados como malos por el test. Estas son las dos métricas con las que se calificará el test.

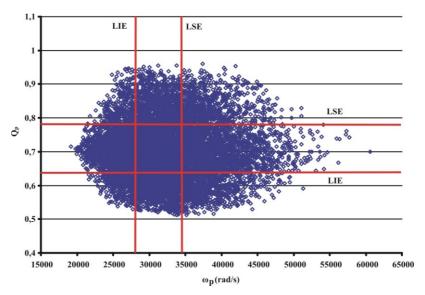

Con el objetivo de demostrar la eficacia de la metodología de desviación de parámetros directos adoptada se muestran en las Figura 4 y Figura 5 los diagramas de dispersión, en los que cada individuo está representado por un punto determinado por sus valores de  $\omega_p$  y  $Q_p$ . También se han indicado en los gráficos los LIEs y LSEs para cada parámetro. Solo aquellos individuos con sus coordenadas dentro de los límites de especificación en  $\omega_p$  y  $Q_p$  son considerados buenos. De las figuras es claro que se han obtenido desviaciones a distintos niveles, tal como se esperaba.

Figura 4: Diagrama de dispersión. Filtro 1

Figura 5: Diagrama de dispersión. Filtro 2

# 5 RESULTADOS OBTENIDOS Y DISCUSIÓN

#### **5.1** Filtro 1

Para este circuito, los mejores resultados para la CF (mayores o iguales al 99%) se obtienen mediante el monitoreo de 3, 4 o 5 atributos de test. Estos casos han sido resaltados en amarillo en la Tabla 3.

Obviamente, si se toman en cuenta los circuitos adicionales necesarios para el test (lo cual impacta en el costo y tiempo de test y en el consumo de potencia), la mejor situación es la de monitorear sólo tres parámetros. Para este caso la cobertura de fallas es excelente, lográndose un esquema de test que tiene una probabilidad de 1% de fallar en la detección de un circuito defectuoso.

No obstante, la consideración única de la cobertura de fallas puede dar una visión parcial del test. Es por este motivo que se ha incluido en el estudio una métrica adicional denominada probabilidad de falsos positivos (PFP), definida como la probabilidad de que un circuito bueno sea declarado como malo por el test. Para los tres casos considerados arriba las PFPs son menores al 8%. Esto significa una situación considerablemente buena, ya que por un lado se obtiene una cobertura excelente a costa de una pérdida de buenos que puede considerarse como relativamente baja. La adopción de alguna de estas opciones se recomienda para aplicaciones de alta criticidad en donde debe prevalecer la capacidad de detección de circuitos malos.

Sin embargo, puede haber situaciones en las que es necesario negociar cobertura de fallas versus probabilidad de falsos positivos. Esto generalmente se da en aplicaciones en las cuales puede tolerarse una menor cobertura a costa de una también menor PFP. Para estos casos, generalmente son importantes las implicancias de las falsas detecciones: costo de mantenimiento innecesario, utilización de recursos redundantes del circuito que podrían haber sido utilizados para otras tareas, tiempo ocioso del circuito, entre otros. En la Tabla 3 se han señalado (en celeste) cuatro casos en los cuales se logra una menor PFP (menores al 3.2%) a costa de reducir en aproximadamente 1% la cobertura de fallas respecto de los casos señalados más arriba. Obviamente, el mejor caso entre estos cuatro considerados es aquel en el que se miden sólo dos atributos de test (Tp y OS) obteniéndose excelentes valores de las dos métricas de evaluación del test consideradas.

| PFP         |       |

|-------------|-------|

| Tr          | 0.70% |

| Тр          | 0.80% |

| Tp+Td       | 0.90% |

| Td          | 0.90% |

| Tp+Tr       | 0.90% |

| Tp+Tr+Td    | 1.00% |

| Td+Tr       | 1.00% |

| OS          | 2.20% |

| Tp+OS       | 3.00% |

| Tp+OS+Tr    | 3.10% |

| Tp+OS+Td    | 3.10% |

| Tp+OS+Tr+Td | 3.20% |

| Ts          | 5.00% |

| Tr+Ts       | 5.70% |

| CF             |       |

|----------------|-------|

| Tp+OS+Ts+Td+Tr | 99,3% |

| Tp+OS+Ts+Td    | 99,3% |

| Tp+OS+Ts       | 99,0% |

| Tp+OS+Ts+Tr    | 99,0% |

| Tp+OS+Tr+Td    | 98,7% |

| Tp+OS+Td       | 98,7% |

| Tp+OS          | 98,1% |

| Tp+OS+Tr       | 98,1% |

| Tp+Ts+Td+Tr    | 95,5% |

| Td+Tr+Ts       | 95,5% |

| Tp+Tr+Ts       | 95,1% |

| Tp+Ts+Td       | 94,2% |

| Td+Ts          | 93,9% |

| Tp+Ts          | 93,8% |

| PFP            |       |

|----------------|-------|

| Tp+Ts          | 5.80% |

| Tp+Ts+Td       | 5.90% |

| Tp+Tr+Ts       | 5.90% |

| Td+Ts          | 5.90% |

| Tp+Ts+Td+Tr    | 6.00% |

| Td+Tr+Ts       | 6.00% |

| Tp+OS+Ts       | 7.20% |

| Tp+OS+Ts+Td    | 7.30% |

| Tp+OS+Ts+Tr    | 7.30% |

| Tp+OS+Ts+Td+Tr | 7.40% |

| CF       |       |

|----------|-------|

| Tr+Ts    | 93,8% |

| Tp+Tr+Td | 81,0% |

| Td+Tr    | 81,0% |

| OS       | 78,6% |

| Tp+Tr    | 78,0% |

| Tp+Td    | 72,4% |

| Ts       | 70,0% |

| Td       | 69,2% |

| Тр       | 69,1% |

| Tr       | 64,3% |

Tabla 3: Valores de PFP y CF. Filtro 1

#### 5.2 Filtro 2

Para este filtro se obtuvo una cobertura de fallas óptima, ya que la probabilidad de detección de un circuito malo alcanza al 100%. Esto se logra en forma indistinta mediante el monitoreo de cuatro o cinco atributos de test (resaltado en amarillo en la Tabla 4). Sin embargo, en estos casos la PFP alcanza el 41%, lo cual puede ser prohibitivamente elevado debido a los motivos ya explicitados para el Filtro 1. Tal como también se ha explicado antes, la reducción de la cobertura de fallas puede dar como resultado una mejor situación en lo que respecta a PFP. En la Tabla 4 se ha resaltado en celeste un grupo de casos para el cual la cobertura de fallas se mantiene en valores elevados (superiores al 99%), pero con menores PFP. Entre este grupo, una situación interesante es la de medición de dos atributos de test (Tp y Ts) que permite obtener una cobertura del 99.1 % que sigue siendo excelente, pero con una PFP de 32.1%.

| PFP      |       |

|----------|-------|

| Ts       | 12.3% |

| Td       | 12.6% |

| Tr       | 17.3% |

| Тр       | 19.8% |

| Tp+Tr    | 19.9% |

| Td+Tr    | 20.0% |

| Tp+Td    | 21.5% |

| Tp+Tr+Td | 21.6% |

| Os       | 22.1% |

| Td+Ts    | 24.7% |

| Tr+Ts    | 29.5% |

| Td+Tr+Ts | 32.1% |

| Tp+Ts    | 32.1% |

| Tp+Tr+Ts | 32.2% |

| Tp+Os    | 32.4% |

| Tp+OS+Tr | 32.4% |

| Tp+Ts+Td | 33.6% |

| CF             |        |

|----------------|--------|

| Tp+OS+Ts+Td    | 100,0% |

| Tp+OS+Ts+Td+Tr | 100,0% |

| Tp+OS+Ts       | 99,8%  |

| Tp+OS+Ts+Tr    | 99,8%  |

| Tp+Ts+Td+Tr    | 99,5%  |

| Td+Tr+Ts       | 99,4%  |

| Tp+Tr+Ts       | 99,3%  |

| Tp+Ts+Td       | 99,2%  |

| Tp+OS+Td       | 99,2%  |

| Tp+OS+Tr+Td    | 99,2%  |

| Tp+Ts          | 99,1%  |

| Tr+Ts          | 98,9%  |

| Tp+Os          | 96,2%  |

| Tp+OS+Tr       | 96,2%  |

| Td+Ts          | 95,3%  |

| Tp+Tr+Td       | 91,8%  |

| Td+Tr          | 90,2%  |

| PFP            |       |

|----------------|-------|

| Tp+Ts+Td+Tr    | 33.6% |

| Tp+OS+Td       | 34.1% |

| Tp+OS+Tr+Td    | 34.1% |

| Tp+OS+Ts       | 39.5% |

| Tp+OS+Ts+Tr    | 39.5% |

| Tp+OS+Ts+Td    | 41.0% |

| Tp+OS+Ts+Td+Tr | 41.0% |

| CF    |       |

|-------|-------|

| Tp+Td | 89,8% |

| Tp+Tr | 82,0% |

| Тр    | 80,0% |

| Tr    | 75,6% |

| Td    | 75,4% |

| Ts    | 72,1% |

| Os    | 64,1% |

Tabla 4: Valores de PFP y CF. Filtro 2

# 6 CONCLUSIÓN

La simplicidad conceptual de TRAM en conjunción con las magnitudes relativamente simples de medir, la hace sumamente atractiva para aplicaciones de test en campo. Para los casos considerados, los resultados de simulación de fallas indican que TRAM puede alcanzar una excelente cobertura de fallas, haciéndola muy interesante para aplicaciones de alta criticidad como las espaciales.

No obstante, debe puntualizarse que ha sido posible observar para uno de los casos considerados una alta probabilidad de falsos positivos. Esto significa que muchos circuitos que son declarados como defectuosos por TRAM tienen una alta probabilidad de ser no defectuosos. Esto puede complicar la aplicación de esta estrategia en situaciones en las que las acciones derivadas de la declaración de un circuito como defectuoso conduzca a una disminución considerable de la operatividad del sistema, a utilización de recursos redundantes que pongan en peligro las características de tolerancia a fallas posteriores y operaciones de mantenimiento costosas, entre otras. Si este es el caso, es recomendable utilizar una segunda estrategia de test para evaluar nuevamente los recursos circuitales que son declarados como defectuosos por TRAM. La adopción de un esquema doble permitiría gozar de los beneficios de la alta cobertura de fallas mostrada en nuestros resultados y compensar la relativamente alta probabilidad de falsos positivos que se han observado en uno de los casos estudiados.

#### REFERENCIAS

Axness C. L., Riewe L., Reber R. A., y Liang A. Y., Radiation characteristics of SIPOS and polysilicon resistors, *IEEE Trans. Nucl. Sci.*, 38:1365-1369, 1991.

Barnaby H. J., Total-Ionizing-Dose Effects in Modern CMOS Technologies, *IEEE Trans. Nucl. Sci.*, 53:3103-3120, 2006.

Bounceur A., Mir S., Simeu E., y Rolíndez L., Estimation of test metrics for the optimisation of analogue circuit testing, *J. Electron Test: Theory Appl*, 23:471-484, 2007.

Calvano J., Alves V., y Lubaszeswski M., Fault detection methodology and BIST method for 2nd order Butterworth, Chebyshev and Bessel approximations. *Proceedings 18th IEEE VLSI Test Symposium*, 319-324, 2000.

Calvano J., Alves V., y Lubaszeswski M., Fault detection methodology for second order filters using compact test vectors transient analysis. *3rd. International Workshop on Design of Mixed-Mode Integrated Circuits and Applications*, 18-24, 1999.

Calvano J., Mesquita Filho A., Castro Alves V., y Lubaszewski M., Faults models and test generation for op amp-the FFM, *J. Electron.Test: Theory Appl.* 27:121–138, 2001.

- Chaehoi A., Latorre L., Azais F., y P. Nouet, Use of a statistical approach for efficient implementation of oscillation based test strategy. *Proceedings 9th International Mixed Signal Test Workshop*, 99-103, 2003.

- Holmes- Siedle A., y Adams L., *Handbook of radiation effects*, Oxford University Press, 2002.

- Kaminska B., Arabi K., Bell I., Goteti P., Huertas J., Kim B., Rueda A., y Soma M., Analog and mixed-signal benchmark circuits-first release. *Proceedings of the International Test Conference*, 183-190, 1997.

- Liu F., y Ozev S., Statistical test development for analog circuits under high process variations", *IEEE Trans. Comput. Aided Des. Integr. Circuits Syst.*, 36: 1465-1477, 2007.

- Mitra A., Fundamentals of Quality Control and Improvement. Prentice Hall, 1998.

- Oldham T. R., y McLean F. B., Total Ionizing Dose Effects in MOS Oxides and Devices, *IEEE Trans. Nucl. Sci.*, 50:483-499, 2003.

- Peralta, J., Peretti, G., Romero, E., y Marqués, C., Evaluación de estrategias de test de circuitos utilizando modelos de fallas estadísticos: un caso de estudio. *Mecánica Computacional*, 26: 2007-2015, 2007.

- Peralta, J., Peretti, G., Romero, E., y Marqués, C., A new performance characterization of transient analysis method. *International Journal of Electronics, Communications and Computer Engineering*, 3:12-19, 2009.

- Raghunathan A., Chun J., Abraham J., y Chatterjee A., Quasi-oscillation based test for improved prediction of analog performance parameters. *Proceedings International Test Conference*, 252-261, 2004.

- Savir J., y Guo Z., Test limitations of parametric faults in analog circuits. *IEEE Trans. Instrum. Meas.*, 52:1444-1454, 2003.

- Schrimpf R., y Fleetwood D., Radiation effects and soft errors in integrated circuits and electronic devices. World Scientific, 2004.